【GexSi1-x/Si异质结器件】

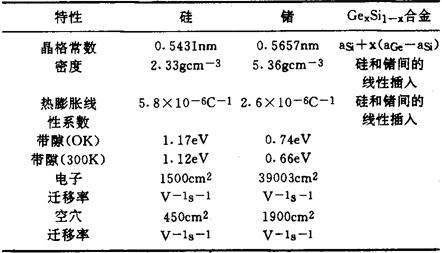

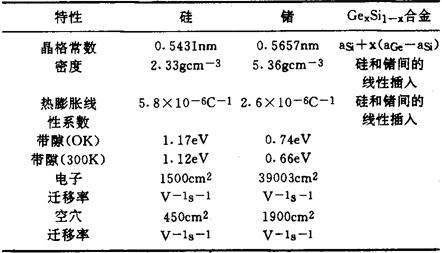

GexSi1-x/Si异质结构器件的研究方兴未艾,已成为能带工程研究的重要内容之一。自80年代初兴起研究Ⅲ-Ⅴ族半导体异质结构材料的热潮并用于器件制作以来,这一领域发展十分迅速,并不断扩大。Ⅱ-Ⅵ族化合物半导体材料及其异质结器件与Ⅲ-Ⅴ族异质结器件一样也深受青睐,正在蓬勃发展。但在半导体产品中,异质结构器件所占的比例仍然极小,造成这一状况的主要原因是占主导地位的半导体硅不能与其它半导体兼容。异质结器件多采用Ⅲ-Ⅴ族和Ⅱ-Ⅵ族化合物半导体材料。尤其是Ⅲ-Ⅴ族极性半导体,是具有高电子迁移率、宽禁带和良好微波性能的半导体材料。分子束外延(MBE)和金属有机物化学汽相淀积(MOCVD)技术的进步促进了其薄膜制备和器件工艺的发展,所制备器件的工作速度和光电特性均优于硅器件。 然而,GaAs等化合物半导体不仅热耗大、成本高,而且目前要制备位错密度小、均匀性好的大直径GaAs单晶还很困难,因此限制了它的广泛应用和发展。硅材料不仅热导性好、机械强度高、缺陷小,而且价格低廉,能获得大直径单晶,同时硅的集成技术已发展到了相当成熟的阶段。硅的同族元素锗也是一种制作工艺技术很完善的半导体材料。因此,利用成熟的硅和锗工艺技术制备应变层超晶格GexSi1-x/Si异质结构材料和器件是完全有可能实现的。早在50年代末期,Glickman,Paul,Warschauer及Dismukers等就开始了对硅锗合金的特性研究工作。1975年,德国Kasper首次在硅衬底上用MBE外延技术生长了高质量的GexSi1-x/Si赝晶层。但由于受到外延生长技术和检测手段等条件的限制,其进展并不大。随着硅MBE外延生长技术的发展,制备高质量GexSi1-x/Si应变层超晶格成为可能。GexSi1-x/Si异质结构材料与硅相比具有可缩小器件尺寸、提高器件工作速度和在同一衬底上集成电子器件和光电子器件等优点。又因为GexSi1-x/Si异质结构器件的制作可以利用成熟的硅集成电路工艺技术,所以这种异质结构的应用领域非常广泛,有着诱人的应用前景,并日益受到人们的重视。GexSi1-x/Si异质结构材料的制备及特性:外延生长。在硅衬底上生长GexSi1-x/Si异质结构的方法很多,如蒸发、分子束外延(MBE)、溅射、原子团束(CB)、化学汽相淀积(CVD)、远距高等离子体增强CVD(RPECVD)、低温CVD(LPCVD)等。目前用得最多的是MBE技术,且进展较快,CVD技术也因其具有产量大、可进行原位掺杂和选择淀积等优点受到人们青睐。蒸发、溅射、MBE以及CB生长技术都采用固体锗作源,而CVD、LPCVD及RPECVD等生长技术却采用锗的气态氢化物作源。总的看来,用MBE生长的材料质量最好,但是生长温度不能高于550℃,否则MBE生长的材料表面就变得粗糙。GexSi1-x/Si系统的失配参数见表,其中给出了硅、锗及GexSi1-x合金的晶格常数、密度、热膨胀线性系数、带隙、电子迁移率及空穴迁移率。通常采用下列公式计算GexSi1-x的晶格常数,即:aGeSi=aSi+(aSi-aGe)=x=ax 式中的a表示晶格常数,x为合金组分,而GexSi1一x合金层的失 配参数fm(x)可用公式 表示。 表示。 表1 硅、锗和GexSi1-x合金的特性

80年代初Bean等用Nomarki光学相衬干涉显微镜研究了Si(100)衬底上生长的GexSi1-x层的表面结构。他们发现生长温度的升高或锗浓度的增加都会引起表面的粗糙或岛状三维生长。1987年Fukuda研究了硅衬底上高纯锗层的表面结构,结果与Bean的发现基本相同。当生长温度超过600℃时,纯锗层的表面就开始变得粗糙,因此在生长GexSi1-x/Si应变层时,如果锗浓度较高,为了避免岛状缺陷的产生,生长温度应严格控制在550℃以下。Englesham和Kvam等在1988年用X射线测量技术分析了在GexSi1-x/Si界面产生的位错,结果令人满意。另一种测量位错密度的有效方法是电子束感生电流(EBIC)技术。生长温度对GexSi1-x/Si应变层临界厚度(hc)的影响很大,生长温度越低,应变层的临界厚度就越大。国外许多研究结果也都证明低温下生长的GexSi1-x/Si应变层的临界厚度较大,当实际厚度与根据平衡理论预测的结果一致时,位错就会集中到有缺陷的地方。因为在外延生长期间这些位错会穿透整个外延层(也会穿透所制作的异质结器件的中心),因此又被称作穿透位错。由此看出,这种穿透位错直接影响着器件的性能,必须设法降低失配外延层中的穿透位错密度。通常采用以下几种方法:(1)将位错面扩展到基片的边缘,或至少要扩展到器件管芯的边界处,以减小位错对器件性能的影响。(2)运用多平面成核机理,提出像应变超晶格这样的结构会导致这些位错平面结合到一起。这样,位错平面每结合一次就会消除一对位错。实验证明这一设想可有效地将极高的穿透位错密度降低到适当的程度,但是这一方法仅对很高的穿透位错密度有效。(3)高温生长一层较厚(约5μm)的组分缓变失配外延层,或者用在氧化物图形上过生长的方法将穿透位错集中到固定的区域内。随着外延技术的发展,利用成熟的硅工艺技术制作新型GexSi1-x/Si异质结器件已经成为可能。GexSi1-x/Si异质结构在器件中的应用将会得到广泛的应用。GexSi1-x/Si异质结双极晶体管(HBT)与其它GexSi1-x/Si异质结器件相比,锗硅HBT起步较早,也是最有希望进入商用领域的硅基异质结器件。由于硅基BHT可有效地改变传统双极晶体管的设计,所以日益受到半导体界的青睐。(1)GexSi1-x/Si HBT的优点。是:由于HBT基区材料的带隙比发射区材料的小,因此不用对发射区进行重掺杂,即使增加基区掺杂也不会降低发射区的注入效率。基区电阻小、噪声低、由注入引起的衰减出现较晚。HBT克服了发射极-基极的隧道效应、击穿电压和结电容增大等问题。发射区注入效率提高,发射区的存储时间降低。基区可做得很薄,这样就降低了渡越时间,提高了频率响应。由于可增加集电区掺杂,使集电极-基极间的空间电荷宽度减小,渡越时间进一步降低,从而又改善了晶体管的频率响应。虽然这会造成集电极-基极结电容较高,但降低基区电阻和渡越时间就可以使结电容得到一定补偿。HBT本征基区和非本征基区的掺杂相同,不必采用特殊的工艺制作非本征基区,由基区“侵蚀”而引起的二维问题得到缓解。HBT还可进行低温工作。HBT还具有其它优点,如集电极和发射极通用、低开启电压和低功耗,器件的截止频率和最高振荡频率都较高,因为数字开关速度和模拟带宽都和这两种频率有关。因此几乎在所有应用领域HBT都优于传统的BJT,其特性明显好于传统BJT,用ALGaAs作发射区,GaAs作基区的HBT已经取得了长足的进步。。而GexSi1-x/Si HBT在诸多方面又都优于GaAlAs/GaAs等的HBT。极其完善的硅隔离技术、化学汽相淀积(CVD)技术、光刻、扩散、离子注入、接触、腐蚀等工艺和集成电路(IC)制作技术都可用于GexSi1-x/Si HBT的制作,而且GexSi1-x/Si异质结的能带结构在HBT中应用也比GaALAs/GaAs优越。1987年Smith和Welbourn等首次成功地研制了GexSi1-x/Si HBT,并在进一步改进器件结构及其性能方面做了大量的研究探索工作。Smith的第1只锗硅HBT是用MBE技术生长的,器件在室温下的电流增益为10~25。1989年人们又将标准的CVD与快速热处理技术相结合制作了高增益BHT。用这种混合快速热处理CVD(RTCVD)技术制作的HBT,其GexSi1-x基区的含锗量为31%。而且尽管基区掺杂水平比邻近的发射区高50倍,但器件的增益仍可达325,这比同质结硅器件的增益至少高出13倍。该HBT的理想因数n=1.03,但如果将基区中的锗含量降到23%,那么理想因数n就为1.01。HBT基区中的少数载流子迁移率对器件的速度有很大影响。如果将基区中锗组分从20%增加到90%,最大振荡频率(fmax)就会由35GHz升高到49GHz。载流子迁移率和基区接触电阻对GexSi1-x/Si HBT的整体性能都有很大影响。IBM研究小组的Patton等人制作了载止频率最高(达75GHz)的GexSi1-x/Si HBT。他们采用低温超高真空CVD技术所制作的HBT中,锗的分布是缓变的,这导致基区中带隙的变化也是缓变的。基区带隙的减小增强了少数载流子的注入作用,使相同结电压下的集电极电流增加,即电流增益的增加及发射极电荷时间常数的减小。GexSi1-x/Si HBT在低温BiCMOS中的应用也很有效。CMOS电路在液氮温度下的性能优良,载流子迁移率高。MOS的阈值电压和线电阻很小。因此电路在低电源电压下可获得高速性能。在室温下BiCMOS的驱动能力比CMOS强,但在低温(液氮温度)下却很不理想。这是因为BiCMOS中的同质结双极晶体管在低温下存在电流增益降低、截止频率下降、发射极-基极间导通电压增加和基区电阻加大等缺点。但如果采用基区为带隙宽度小的GexSi1-x/Si HBT就可有效地避免上述问题。低温下GexSi1-x/Si HBT的电流增益可随温度的降低而增加。休斯航空公司采用MBE技术制作了n-p-n Si/GexSi1-x/Si HBT。器件在室温和10K温度下工作特性良好,最好的室温增益是40。所用的掺杂剂为硼、锑和镓,发射区和基区掺杂浓度分别是5×1023m-3和6×1024m-3。这样就可达到降低基区薄层电阻和发射极-基级电容的目的。在低于10K的极低温度条件下,尽管器件的增益随温度的降低有微弱的减小,但这比最好的硅双极晶体管在低温下的增益下降要低得多。由此看出,Si/GexSi1-x/Si HBT是用作红外FPA系统中低噪声、高性能读出电路和信号处理电路的理想元件。在过去双极晶体管已有了一定程度的改进,但主要局限在器件横向尺寸和纵向尺寸的减小上,其工作原理并无多大改变。用多晶硅材料连结非本征发射区和基区,降低了双极晶体管的横向寄生时间常数。但限制进一步提高硅双极晶体管开关特性的因素主要是垂直穿过晶体管中性基区的载流子渡越时间。Taylor和Simmons等设计了一种新型器件,即BICFET。这种BICFET实际是单极晶体管,除很窄的区域为p型掺杂外,该器件基本是n型掺杂。为了避免因能带弯曲而形成电中性基区,p型区要做得很窄。负的受主电荷薄层起热离子势垒的作用,即使在集电极上加了正偏压,它也能阻止电子的流动。集电区电流,由反型沟道中的空穴浓度来控制。这种BICFET在300K温度下测得的电流密度jc=2.5×104A/cm2,增益是365,这也是BICFET器件达到的最高增益。用Ⅲ-Ⅴ族半导体材料制作的p沟BICFET,在室温下的增益仅为8~15。因此Ⅲ-Ⅴ族半导体异质结构并不是制作p沟道BICFET器件的理想材料。而GexSi1-x/Si异质结构不仅增益大,而且还可有效地避免电荷存储和载流子复合等问题,确实是一种很有前途的高速器件。用GexSi1-x/Si应变层制作的MODFET已有n沟器件和p沟器件两种。p沟GexSi1-x/SiMODFEГ是采用标准的硅工艺技术制作的。为了防止缺陷的产生应保持低的生长温度。Ge0.2Si0.8应变层被夹在两层的10-7m厚的p+硅层之间。p+层中的空穴迁移到Ge0.2Si0.8层中,形成高迁移率二维电子气。器件的源极和漏极是用离子注入BF2的方法形成的,用电子束蒸发钛(Ti)实现了栅极的金属化,用低温水汽氧化对器件进行钝化,最后进行CVD绝缘淀积。这种p沟GexSi1-x/Si MODFET在300K温度下的跨导达9S/m。n沟GexSi1-x/Si MODFET器件制作方法为:首先在高电阻率Si(100)衬底上淀积非应变Ge0.25Si0.75缓冲层,然后在这一非应变缓冲层上制作n沟器件。应变层依次为:2×10-8非掺杂硅层(该层的中心为锑(Sb)掺杂的Ge0.5Si0.5尖峰)、10-8m缓变层(x在0.5和0之间)和10-8非掺杂表面硅层。Pt-Ti-Au结构构成了高质量的肖特基栅。器件的非本征跨导达36S/m。GexSi1-x/Si异质结构在谐振隧道二极管、NERFET和LED中的应用研究还只是刚刚起步,但对未来器件结构的设计有着重要的启发意义。GexSi1-x/Si谐振隧道结构二极管在适当偏压下,GexSi1-x/Si包封层中的空穴会通过中心合金量子阱中的束缚态进入另一个包封层,在低温下可产生隧道效应。电压为0.4V时首次出现微弱的隧道效应,第二次隧道效应产生于0.7V,并同时出现负微分特性。4.2K温度时,峰谷之比是2.1∶1,这与ALGaAs/GaAs30∶1的峰谷比虽然相差甚远,但随着GexSi1-x/Si材料系统特性的改进及工艺水平的提高,这一峰谷比会得到改善。该结构在谐振隧道器件中的应用前景会逐步明朗。NERFET是利用GexSi1-x沟道中热载流子发射特点而制作的一种新型器件。实际上NERFET是一种浮置隐埋栅极FET。空穴分布在p型GexSi1-x/Si沟道中,沟道的表面上覆盖着一层本征硅,这样,沟道就将注入形成的源极和漏极连结起来,沟道下面是n-p-n叠层。在低源——漏偏压下,电导会增加,使载流子的能量变得很高并越过势垒到达n型硅附近,落入浮置的p型硅层中。为使GexSi1-x/Si沟道耗尽,该浮置层应带电。这样77K下的源漏电流就会产生2∶1的负微分电阻。由于负微分电阻取决于浮置层的带电量,因此这种器件非常适合制作存储元件。GexSi1-x/Si LED器件的研究也正在引起人们的注意,相信会取得突破性的发展。虽然频率达100GHz的全硅碰撞电离雪崩渡越时间(IMPATT)二极管业已研制成功,但其工作特性并不理想。高频下该二级管的效率会急剧下降而且噪声极大。多方面的研究结果表明,在强电场区中用窄带隙材料可使电离发生在低电场区,从而可提高器件效率。低电场下隧道注入和碰撞电离的复合会产生新的异质结构,即MITATT二极管。Luy等制作了频率达103GHz的MITATT,该器件在低噪声条件下输出为25mW。如果进行优化设计,可进一步提高输出功率、降低噪声。CMOS电路的性能很大程度上受到PMOS管低跨导的制约。一种较理想的解决方法就是在PMOS管的栅下设计GexSi1-x埋层来提高空穴迁移率从而增大PMOS管的跨导。这种结构从以下两个方面提高了空穴的迁称率:(1)反型层不是在Si/SiO2界面而是在GexSi1-x层中形成的,且与界面隔有一层硅缓冲层,这样减小了表(界)面散射对空穴迁移率的影响。(2)硅锗层中应力提高了空穴的迁移率。锗和硅之间的晶格失配率达4.17%,应变使应变层的带隙大为降低。当x>0.5时,GexSi1-x/Si应变层的带隙低于纯锗,这就意味着GexSi1-x/Si有可能成为用于光纤通信的1.3μm和1.55μm红外光电探测器的理想材料。1984年Luryi首次在硅片上成功地制作了锗PIN光电探测器,波长范围为1.3~1.5μm,量子效率达40%。由于层结构并非假晶,因此其暗电流和噪声系数都较高。1986年Temkin等制作了吸收区为20个周期超晶格的PIN探测器。每一周期都由一个6nm厚的Ge0.6Si0.4阱和一个2.9nm厚的硅势垒组成。超晶格是在厚度为1μmAs原子掺杂为5×1022m-3的n型Si(100)缓冲层上生长的,表面是一层1μm厚的B原子掺杂为5×1016cm-3p型硅层,最后在其表面上淀积p+硅接触薄层。该探测器的击穿电压为30~38V,其它电特性也不错。与此同时,Pearsall制作了GexSi1-/Si超晶格雪崩倍增光电二极管(APD),各项性能指标也较令人满意。GexSi1-x/Si异质结器件虽然起步较晚,但它一问世就引起广泛的注意,并有很大进展。随着GexSi1-x/Si材料质量、特性和提高检测手段的不断完善,应用领域将会不断扩大。(机械电子部第13研究所李秀清撰) |

表示。

表示。